邏輯門(mén)主要使用二極管或晶體管作為電子開(kāi)關(guān)來(lái)實(shí)現(xiàn),但也可以使用真空管、電磁繼電器(繼電器邏輯)、流體邏輯、氣動(dòng)邏輯、光學(xué)、分子甚至機(jī)械元件來(lái)構(gòu)建。通過(guò)放大,邏輯門(mén)可以以與組合布爾函數(shù)相同的方式級(jí)聯(lián),允許構(gòu)建所有布爾邏輯的物理模型。邏輯器件包括多路復(fù)用器、寄存器、算術(shù)邏輯單元(ALU) 和計(jì)算機(jī)存儲(chǔ)器等設(shè)備,一直到完整的微處理器,其中可能包含超過(guò)1億個(gè)門(mén)。在現(xiàn)代實(shí)踐中,大多數(shù)柵極由MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管)制成。

1.邏輯門(mén)的概念

1.1基本單元

邏輯門(mén)(LogicGates)是在集成電路(IntegratedCircuit)上的基本組件。簡(jiǎn)單的邏輯門(mén)可由晶體管組成。這些晶體管的組合可以使代表兩種信號(hào)的高低電平在通過(guò)它們之后產(chǎn)生高電平或者低電平的信號(hào)。高、低電平可以分別代表邏輯上的“真”與“假”或二進(jìn)制當(dāng)中的1和0,從而實(shí)現(xiàn)邏輯運(yùn)算。邏輯門(mén)又稱(chēng)“數(shù)字邏輯電路基本單元”。執(zhí)行“或”、“與”、“非”、“或非”、“與非”等邏輯運(yùn)算的電路。任何復(fù)雜的邏輯電路都可由這些邏輯門(mén)組成。廣泛用于計(jì)算機(jī)、通信、控制和數(shù)字化儀表。

1.2作用

通過(guò)控制高、低電平(分別代表邏輯上的“真”與“假”或二進(jìn)制當(dāng)中的“1”和“0”),從而實(shí)現(xiàn)邏輯運(yùn)算。

2.邏輯門(mén)的種類(lèi)

常見(jiàn)的邏輯門(mén)包括“與”門(mén),“或”門(mén),“非”門(mén),“異或”(也稱(chēng):互斥或)等等。邏輯門(mén)可以組合使用實(shí)現(xiàn)更為復(fù)雜的邏輯運(yùn)算。

2.1或門(mén)

或門(mén)(英文:Or gate)又稱(chēng)或電路。如果幾個(gè)條件中,只要有一個(gè)條件得到滿(mǎn)足,某事件就會(huì)發(fā)生,這種關(guān)系叫做“或”邏輯關(guān)系。具有“或”邏輯關(guān)系的電路叫做或門(mén)?;蜷T(mén)有多個(gè)輸入端,一個(gè)輸出端,多輸入或門(mén)可由多個(gè)2輸入或門(mén)構(gòu)成。只要輸入中有一個(gè)為高電平時(shí)(邏輯1),輸出就為高電平(邏輯1);只有當(dāng)所有的輸入全為低電平時(shí),輸出才為低電平。

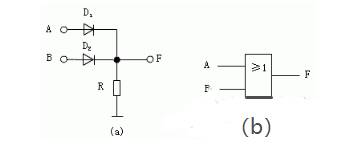

“或”門(mén)可以有兩個(gè)或者兩個(gè)以上輸入端和一個(gè)輸出端。由二極管構(gòu)成的兩輸入“或”門(mén)電路如圖1(a)所示,與其對(duì)應(yīng)的邏輯符號(hào)如圖1(b)所示。

圖1二極管或門(mén)電路及或門(mén)邏輯符號(hào)

圖1(a)中,A、B為輸入端,F(xiàn)為輸出端。該電路根據(jù)輸入信號(hào)取值的不同,同樣可分為如下兩種工作情況。

①當(dāng)兩個(gè)輸入端電壓VA、VB均為低電平0V時(shí),二極管D1、D2均截止,輸出端電壓VF=0V。

②當(dāng)兩個(gè)輸入端電壓VA、VB均為+5V,或者其中的一個(gè)+5V時(shí),輸入為+5V的二極管將處于導(dǎo)通狀態(tài),從而使得輸出端F的電壓為高電平,即VF≈+5V。

顯然,該電路實(shí)現(xiàn)“或”運(yùn)算的邏輯功能,輸出F和輸入A、B之間的邏輯關(guān)系表達(dá)式為F=A+B。

2.2與門(mén)

與門(mén)(英語(yǔ):AND gate)又稱(chēng)“與電路”。是執(zhí)行“與”運(yùn)算的基本邏輯門(mén)電路。有多個(gè)輸入端,一個(gè)輸出端。當(dāng)所有的輸入同時(shí)為高電平(邏輯1)時(shí),輸出才為高電平,否則輸出為低電平(邏輯0)。

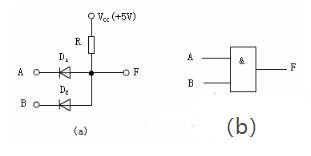

“與”門(mén)有兩個(gè)以上輸入端和一個(gè)輸出端。圖2(a)給出了由二極管組成的兩輸入“與”門(mén)電路,與其對(duì)應(yīng)的邏輯符號(hào)如圖2(b)所示。圖2(a)中,A、B為輸入端,F(xiàn)為輸出端。該電路根據(jù)輸入信號(hào)取值的不同,同樣可分為如下兩種工作情況。

圖2 二極管與門(mén)電路及與門(mén)邏輯符號(hào)

①當(dāng)兩個(gè)輸入端電壓VA、VB均為低電平0V時(shí),二極管D1、D2均截止,輸出端電壓VF=0V。

②當(dāng)兩個(gè)輸入端電壓VA、VB均為+5V,或者其中的一個(gè)+5V時(shí),輸入為+5V的二極管將處于導(dǎo)通狀態(tài),從而使得輸出端F的電壓為高電平,即VF≈+5V。

顯然,該電路實(shí)現(xiàn)“或”運(yùn)算的邏輯功能,輸出F和輸入A、B之間的邏輯關(guān)系表達(dá)式為F=A+B。

2.3非門(mén)

非門(mén)(英文:NOT gate)又稱(chēng)反相器,是邏輯電路的基本單元,非門(mén)有一個(gè)輸入和一個(gè)輸出端。邏輯符號(hào)中輸出端的圓圈代表反相的意思。當(dāng)其輸入端為高電平(邏輯1)時(shí)輸出端為低電平(邏輯0),當(dāng)其輸入端為低電平時(shí)輸出端為高電平。也就是說(shuō),輸入端和輸出端的電平狀態(tài)總是反相的。

2.4與非門(mén)

由與門(mén)與非門(mén)組合而成。

2.5或非門(mén)

由或門(mén)和非門(mén)組合而成。其中,非門(mén)和或非門(mén)在數(shù)字電路中較為常見(jiàn)。

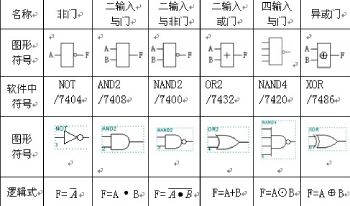

3.邏輯門(mén)符號(hào)表

圖3 邏輯門(mén)符號(hào)圖

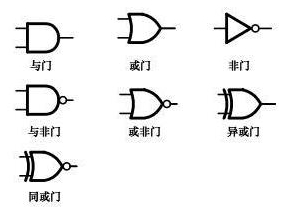

4.邏輯門(mén)的電路符號(hào)圖

把基本邏輯運(yùn)算的電子電路稱(chēng)之為邏輯門(mén)電路。在數(shù)字電路關(guān)系應(yīng)用中,邏輯門(mén)電路中的門(mén)代表著基本邏輯關(guān)系的電路。通過(guò)對(duì)邏輯門(mén)內(nèi)部電路的源器件的差異,我們可以將其分為三大類(lèi),比較常用的就是CMOS的邏輯門(mén)電路。這種CMOS邏輯門(mén)電路具備良好的應(yīng)用效益,首先其功耗比較低,具備較低的應(yīng)用成本,其電源電壓的范圍比較寬,邏輯度比較高,具備較強(qiáng)的抗干擾能力,其輸入阻抗比較高。MOS門(mén)電路是由一系列的單極型MOS管構(gòu)成,其具備比較簡(jiǎn)單的制造工藝,其功耗水平比較低,具備較高的集成度,其抗干擾能力強(qiáng),比較適合進(jìn)行大規(guī)模集成電路的應(yīng)用。

在實(shí)踐過(guò)程中,MOS門(mén)電路按照其MOS管的應(yīng)用不同,進(jìn)行不同類(lèi)型的劃分。CMOS電路的應(yīng)用優(yōu)點(diǎn)比較特殊,其靜態(tài)功耗比較低,抗干擾能力強(qiáng),工作具備較高的穩(wěn)定性,其開(kāi)關(guān)速度也是比較高的,因此其應(yīng)用性比較廣泛。在數(shù)字電路應(yīng)用中,邏輯門(mén)電路是一種基本的邏輯元件。邏輯門(mén)的中就是一種開(kāi)關(guān),在一定條件的建立下,其決定信號(hào)的通過(guò)或者不通過(guò)。在實(shí)際運(yùn)作中,我們可以看到門(mén)電路輸入及其輸出存在密切的因果關(guān)系,我們把門(mén)電路稱(chēng)之為邏輯門(mén)電路,其基本邏輯關(guān)系是非、或、與關(guān)系。

圖4 邏輯門(mén)電路符號(hào)圖

5.邏輯門(mén)的常見(jiàn)問(wèn)題

5.1邏輯門(mén)的作用是什么?

邏輯門(mén)用于做出決策,以便在應(yīng)用正確的邏輯序列時(shí)“打開(kāi)”電氣輸出。每個(gè)邏輯門(mén)都有一個(gè)名稱(chēng),有助于描述不同的輸入將如何確定可能的輸出。

5.2誰(shuí)發(fā)明了邏輯門(mén)?

巧合電路的發(fā)明者WaltherBothe因1924年第一個(gè)現(xiàn)代電子與門(mén)獲得了1954年諾貝爾物理學(xué)獎(jiǎng)。KonradZuse為他的計(jì)算機(jī)Z1(1935年至1938年)設(shè)計(jì)并制造了機(jī)電邏輯門(mén)。

5.3AND門(mén)如何工作?

AND門(mén)是一個(gè)基本的數(shù)字邏輯門(mén),它實(shí)現(xiàn)了數(shù)學(xué)邏輯中的邏輯與(∧)——它根據(jù)真值表運(yùn)行。只有當(dāng)與門(mén)的所有輸入都是高電平(1)時(shí),才會(huì)產(chǎn)生高電平輸出(1)。如果與門(mén)的所有輸入都沒(méi)有或不是全部為高電平,則結(jié)果為低電平輸出。

5.4共有多少個(gè)邏輯門(mén)?

共有七個(gè)基本邏輯門(mén):AND、OR、XOR、NOT、NAND、NOR和XNOR。AND門(mén)之所以如此命名是因?yàn)槿绻?被稱(chēng)為“假”而1被稱(chēng)為“真”,則該門(mén)的作用與邏輯“與”運(yùn)算符相同。

5.5與非門(mén)如何工作?

在數(shù)字電子學(xué)中,與非門(mén)(NOT-AND)是一個(gè)邏輯門(mén),它產(chǎn)生的輸出只有在所有輸入都為真時(shí)才為假,因此它的輸出是對(duì)與門(mén)的輸出的補(bǔ)充。只有當(dāng)門(mén)的所有輸入都是高(1)時(shí),才會(huì)產(chǎn)生低(0)輸出,如果任何輸入為L(zhǎng)OW(0),則結(jié)果為HIGH(1)輸出。

5.6什么是計(jì)算機(jī)科學(xué)中的邏輯門(mén)?

邏輯門(mén)是一系列連接在一起以提供一個(gè)或多個(gè)輸出的晶體管,每個(gè)輸出都基于提供給它的輸入或輸入組合。

結(jié)語(yǔ)

以上就是邏輯門(mén)種類(lèi)及電路圖的介紹了,自1990年代以來(lái),大多數(shù)邏輯門(mén)采用CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)技術(shù)制造,該技術(shù)同時(shí)使用NMOS和PMOS晶體管。通常數(shù)以百萬(wàn)計(jì)的邏輯門(mén)被封裝在一個(gè)集成電路中。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專(zhuān)業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專(zhuān)業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹