隨著SOC(SystemonChip)的迅速發(fā)展,使用深亞微米標(biāo)準(zhǔn)CMOS工藝的模擬集成電路的設(shè)計(jì),已成為當(dāng)前芯片設(shè)計(jì)的一種趨勢(shì)。CMOS運(yùn)算放大器是模擬電路中重要基本單元,該單元不但要具有傳統(tǒng)運(yùn)放的基本特性,如高增益、低失調(diào)等;而且隨著低電源電壓的要求,還必須具備接近于供電電源電壓和地之間(軌對(duì)軌)的輸入共模范圍和輸出擺幅。因此文中基于0.6mCMOS工藝,設(shè)計(jì)了一種軌對(duì)軌運(yùn)算放大器。該運(yùn)算放大器采用了3.3V單電源供電,其輸入共模范圍和輸出信號(hào)擺幅接近于地和電源電壓。

1.軌對(duì)軌運(yùn)放輸入級(jí)的原理

由傳統(tǒng)的差分放大器的直流特性可知,通過適當(dāng)?shù)剡x擇放大器的直流電流和器件特性參數(shù),對(duì)于NMOS差分輸入放大電路可以使其共模輸入范圍的上限值接近于電源電壓VDD,但下限值電位距離地參考點(diǎn)很遠(yuǎn),達(dá)不到軌對(duì)軌運(yùn)放輸入級(jí)的軌對(duì)軌的共模輸人的要求。同樣,對(duì)于PMOS差分輸入放大電路可以使其共模輸入范圍的下限值接近于地參考點(diǎn),而上限值距離V很遠(yuǎn),同樣也不能滿足軌對(duì)軌的共模輸入的要求。注意到兩種差分輸入放大電路對(duì)于共模輸入范圍的互補(bǔ)特性,可將兩種電路并連作為運(yùn)算放大器的輸入級(jí),這樣該輸入級(jí)的共模輸入范圍可滿足運(yùn)放輸入級(jí)軌對(duì)軌的要求。

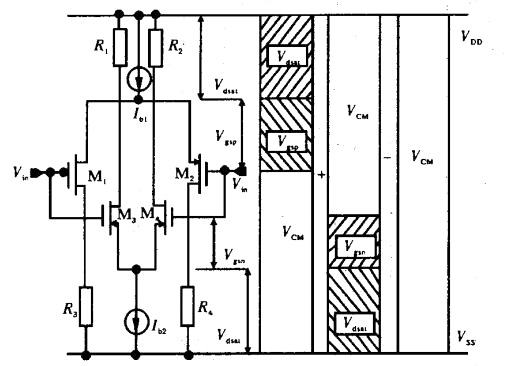

圖1 軌對(duì)軌輸入級(jí)電路

互補(bǔ)式運(yùn)放差分輸入電路如圖1所示。從圖中可以看出,如果NMOS差分對(duì)單獨(dú)工作時(shí),NMOS差分對(duì)管M1,M2的輸入共模范圍為VDD~Vgsn+Vdsat ;如果 PMOS差分對(duì)單獨(dú)工作時(shí),PMOS差分對(duì)管M3,M4的輸入共模范圍為Vss~Vsp+Vdsat;所以兩種差分電路并聯(lián)時(shí)的輸入共模范圍為Vss~VDD,滿足了軌對(duì)軌輸入共模電壓范圍的要求,輸入級(jí)的最小電源電壓為:

式中,Vgsp為PMOS管的柵源電壓;Vsn為NMOS管的柵源電壓; Vdsat為采用電流鏡作為PMOS差分對(duì)和NMOS差分對(duì)尾電流管的飽和電壓,即電流源兩端的電壓(這里假設(shè)PMOS差分對(duì)和NMOS差分對(duì)尾電流相等)。

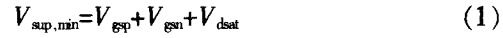

但是將PMOS差分對(duì)和NMOS差分對(duì)簡(jiǎn)單地并聯(lián)構(gòu)成軌對(duì)軌的輸入電路,該電路并不能很好地工作。將該輸入電路工作狀態(tài)根據(jù)共模輸人電壓的不同簡(jiǎn)單分成3個(gè)區(qū)域,假設(shè)K=1/2·Kn·(W/L)n=1/2·Kp·(W/L)p;而且兩個(gè)PMOS差分對(duì)和NMOS差分對(duì)尾電流相等,即PMOS差分對(duì)尾電流Ip和NMOS差分對(duì)尾電流Ip相等,In=Ip=I,則:

式中,gmn腳為NMOS差分對(duì)的跨導(dǎo);gmp為PMOS差分對(duì)的跨導(dǎo)。

區(qū)域I:當(dāng)共模輸入電壓接近于電源電壓VDD時(shí),NMOS差分對(duì)處于放大工作狀態(tài),PMOS差分對(duì)處于截止?fàn)顟B(tài),則輸入電路的跨導(dǎo)為gm。

區(qū)域Ⅱ:當(dāng)共模輸入電壓接近于電源電壓Gnd時(shí),PMOS差分對(duì)處于放大工作狀態(tài),NMOS差分對(duì)處于截止?fàn)顟B(tài),則輸入電路的跨導(dǎo)為gmn。

區(qū)域Ⅲ:當(dāng)共模輸入電壓處于電源電壓的一半時(shí),PMOS和NMOS差分對(duì)同時(shí)處于放大工作狀態(tài),則輸入電路的跨導(dǎo)為gmn+gmp=2gmn。

所以,在整個(gè)軌對(duì)軌的共模輸入電壓范圍內(nèi),運(yùn)放的輸入電路的跨導(dǎo)的最大值是其最小值的二倍。由于輸入電路的跨導(dǎo)的不同,會(huì)導(dǎo)致在共模輸入電壓范圍內(nèi)運(yùn)算放大器的增益不同,在相同輸入信號(hào)頻率下相頻的反應(yīng)也會(huì)不同,所以輸出信號(hào)在不同的共模輸入電壓下產(chǎn)生失真,對(duì)于整個(gè)電路的相位補(bǔ)償會(huì)相當(dāng)困難,并且有可能導(dǎo)致運(yùn)算放大器工作的不穩(wěn)定。

根據(jù)已有文獻(xiàn),可以采用較好地解決該問題的方法如下:

(1)PMOS和NMOS差分對(duì)工作于亞閾區(qū),采用控制電路控制NMOS差分對(duì)尾電流和PMOS差分對(duì)尾電流之和為常數(shù)。

(2)采用平方根電路控制NMOS差分對(duì)尾電流的平方根值與PMOS差分對(duì)尾電流的平方根值之和為常數(shù)。

(3)采用尾電流開關(guān)控制電路控制PMOS和NMOS差分對(duì)尾電流。

(4)采用齊納二極管,用來保持Vgsn+|Vgsp|為常數(shù)。

(5)采用電平移動(dòng)電路來改變輸入差分電路的輸入電平。

不種方法具有不同的優(yōu)缺點(diǎn).文中的運(yùn)算放大器輸入電路采用的是第三種方法。

2.輸入差分對(duì)管尾電流控制式

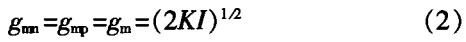

輸入差分對(duì)管尾電流控制式軌對(duì)軌運(yùn)算放大器如圖2所示。從前面的分析可知,當(dāng)輸入共模電壓為中間值時(shí)的輸入差分電路的跨導(dǎo),為其輸入共模電壓在共模輸入范圍的最大值或最小值時(shí)的輸入差分電路跨導(dǎo)的兩倍,即gmn+gmp=2gmn=2·(2KI)。所以,只要使兩個(gè)差分對(duì)單獨(dú)工作時(shí)的尾電流為其同時(shí)工作時(shí)的尾電流的4倍,就能保證共模輸入電壓在軌對(duì)軌的共模輸入范圍內(nèi)輸入級(jí)的跨導(dǎo)穩(wěn)定。

圖2 輸入差分對(duì)管尾電流控制式軌對(duì)軌運(yùn)算放大器

如圖2所示。電路包含兩個(gè)分別由開關(guān)管控制的放大倍數(shù)為1:3的電流鏡M13~M14,M8~M7。在輸入共模電壓在很低范圍內(nèi)時(shí),輸入級(jí)N管差分對(duì)截止,電流開關(guān)M15閉和,NMOS對(duì)管的尾電流被M15引到由M13和M14組成的1:3的電流鏡,從而使PMOS管差分對(duì)的尾電流等于原來的4倍。同理,在輸入共模電壓在接近電源電壓VDD范圍內(nèi)時(shí),P管差分對(duì)截止,通過開關(guān)管控制的1:3的電流鏡。N管差分對(duì)的尾電流為原來的4倍。在輸入共模電壓處于中間范圍內(nèi),兩對(duì)差分對(duì)管同時(shí)導(dǎo)通,控制開關(guān)M15和M14都斷開,兩對(duì)開關(guān)控制的電流鏡都不工作,因此實(shí)現(xiàn)了在軌對(duì)軌的輸入共模范圍內(nèi),輸入級(jí)的跨導(dǎo)基本相同。

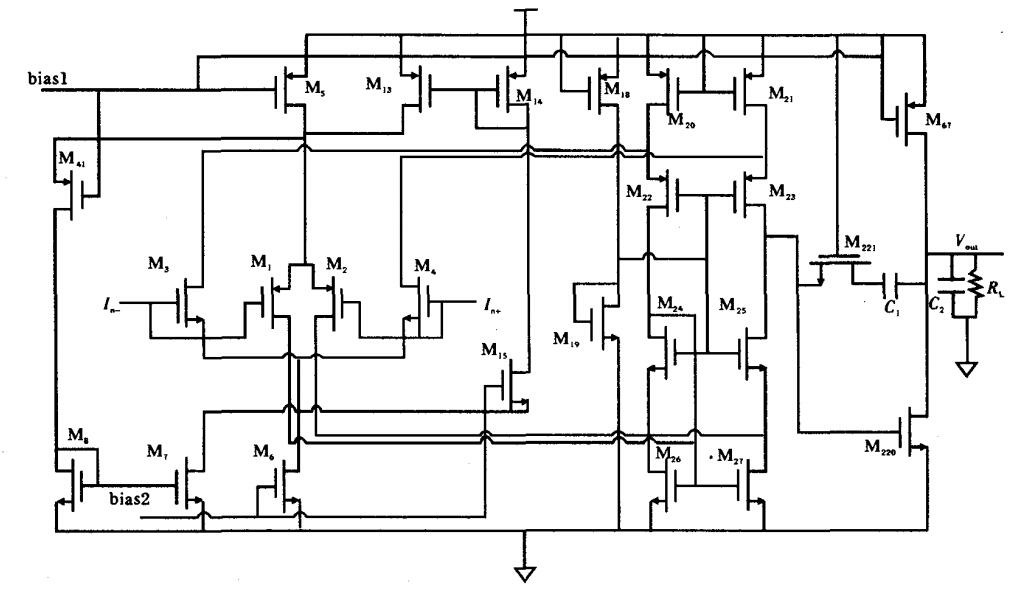

3.仿真分析

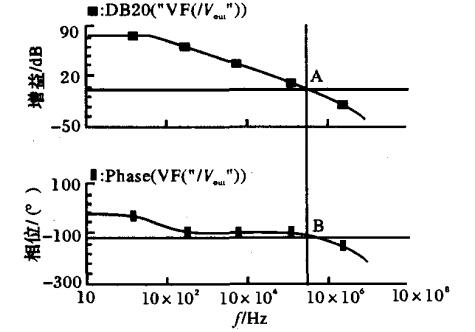

采用Cadence Spectre工具對(duì)輸入差分對(duì)管尾電流控制式軌對(duì)軌運(yùn)算放大器進(jìn)行仿真分析,所得到的頻率響應(yīng)特性曲線如圖3所示。

圖3 頻率響應(yīng)特性曲線

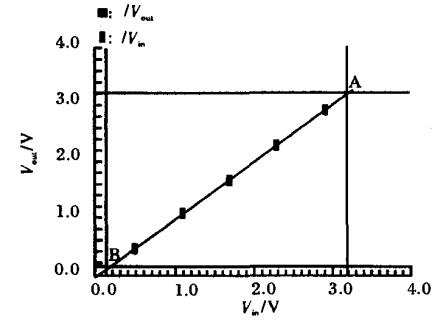

圖4 單位增益?zhèn)鬏斕匦郧€

圖3表明,該運(yùn)放在電源電壓3.3V.輸入共模電壓為1.65V,負(fù)載電阻100kΩ,負(fù)載電容5pF時(shí),其低頻增益為77dB,單位增益帶寬為4.32MHz,相位裕度為79°。靜態(tài)功耗為 1.4mW。 圖4為該運(yùn)算放大器的單位增益?zhèn)鬏斕匦郧€,該測(cè)試是將運(yùn)放接成電壓跟隨器的方式 ,通過輸入端 的DC掃描 ,測(cè)量運(yùn)放的單位增益響應(yīng)。從圖4可得到,運(yùn)放的輸入輸出的線性度基本達(dá)到了軌對(duì)軌的電壓范圍。另外 。通過對(duì)該運(yùn)放的瞬態(tài)分析得到,運(yùn)放的正負(fù)轉(zhuǎn)換率分別為SR+=3.624V/μs,SR-=3.63V/μs。

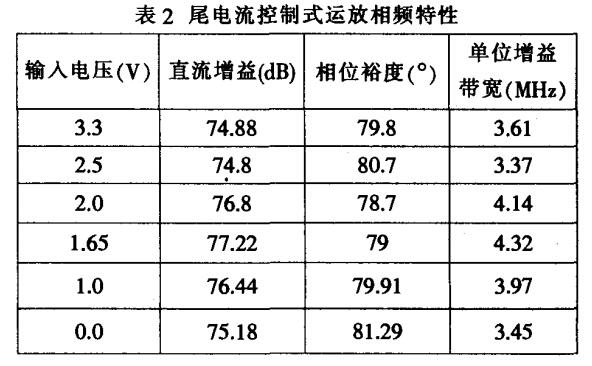

該運(yùn)放的性能參數(shù)分別如表1所示,表2所示為在不同的輸入電壓下,運(yùn)放的小信號(hào)放大倍數(shù)。

其小信號(hào)增益最大誤差為2.34dB.相位裕度最大誤差為2.59°,單位增益帶寬最大誤差為0.87MHz。

結(jié)束語

以上就是基于軌對(duì)軌CMOS運(yùn)算放大器的設(shè)計(jì)的介紹。該運(yùn)放具有結(jié)構(gòu)簡(jiǎn)單,低功耗,高增益和較好的輸入、輸出軌對(duì)軌特性。該放大器包括輸入級(jí)采用帶有跨導(dǎo)控制電路的互補(bǔ)差分對(duì)結(jié)構(gòu).輸入級(jí)的輸出采用折疊式寬擺幅共源共柵求和電路.輸出級(jí)采用具有相位補(bǔ)償?shù)腜MOS為負(fù)載的共源級(jí)電路。從仿真結(jié)果表明,尾電流控制式軌對(duì)軌運(yùn)放從性能結(jié)構(gòu)上非常適用于低壓低功耗應(yīng)用。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹