電容去耦是電源完整性(Power Integrity,PI)設(shè)計(jì)里面很重要的一部分,而PI設(shè)計(jì)則是為了保證電源分配網(wǎng)絡(luò)(Power Distribution Network,PDN)系統(tǒng)能夠滿足負(fù)載芯片對(duì)電源的要求。

PDN主要作用:1、為負(fù)載提供干凈的供電電壓;2、為信號(hào)提供低噪?yún)⒖悸窂健?/div>

電源噪聲

電源噪聲有啥影響,打個(gè)極端的比方,IC的高電平判決門限是1.2V,我的電源噪聲是1.3V,當(dāng)我噪聲傳遞到了這個(gè)IC的時(shí)候,噪聲會(huì)造成誤判決。大部分時(shí)候沒有這么嚴(yán)重,但是噪聲會(huì)影響系統(tǒng)的可靠性和穩(wěn)定性。

而對(duì)于噪聲抑制,在設(shè)計(jì)的時(shí)候,并不是等著噪聲出現(xiàn)了之后再去想辦法消除或者是減輕它,做硬件的同學(xué)們應(yīng)該知道,問題出現(xiàn)后再去解決,這樣代價(jià)是非常大的。一般都是在設(shè)計(jì)之初就把各種預(yù)防措施都考慮進(jìn)去,盡可能的規(guī)避掉可能會(huì)發(fā)生的問題,不要幻想著可以試錯(cuò)(這可就是改板了,那都是經(jīng)費(fèi)呀)。

電源噪聲的來源:

1、硬件本身引入的,比如說穩(wěn)壓電源的紋波,當(dāng)前穩(wěn)壓電源分為線性電源和開關(guān)電源,線性電源的紋波較小,開關(guān)電源的紋波較大,對(duì)于電源噪聲敏感的電路一般不建議使用開關(guān)電源(不過隨著技術(shù)的提升感覺現(xiàn)在開關(guān)電源紋波也能做的很小了);

2、電源無法實(shí)時(shí)的響應(yīng)負(fù)載電流需求,一般電源依據(jù)負(fù)載的功耗需求需要實(shí)時(shí)的對(duì)輸出電流進(jìn)行調(diào)整,否則當(dāng)負(fù)載功耗增大的時(shí)候,會(huì)導(dǎo)致電源輸出電壓被拉低。但是對(duì)于電源本身,是有一個(gè)調(diào)整響應(yīng)時(shí)間的,一般是us級(jí),所以,當(dāng)負(fù)載電流瞬態(tài)變化頻率超過這一范圍的時(shí)候,穩(wěn)壓電源無法及時(shí)響應(yīng),就會(huì)造成鏈路上電壓出現(xiàn)跌落,這也是電源噪聲的一種;

3、板上壓降,有路徑的地方就有阻抗,有負(fù)載就會(huì)有電流,有電流有阻抗就會(huì)有壓降。加上PCB上的各種寄生參數(shù),寄生電感和寄生電容對(duì)頻率敏感,而負(fù)載功耗一般也是動(dòng)態(tài)變化的,具有交流特性,兩者一結(jié)合就造成的負(fù)載端電壓的波動(dòng),由阻抗產(chǎn)生的噪聲,也是電源噪聲的一種;

4、PCB層間噪聲,PCB是有多層的,信號(hào)在傳輸穿過不同平面的同時(shí)會(huì)產(chǎn)生返回信號(hào),信號(hào)有時(shí)候來不及通過去耦電容進(jìn)行換層,就只能通過耦合的方式進(jìn)行換層,對(duì)于不同的平面來說就相當(dāng)于電容在進(jìn)行充放電,引起局部噪聲(實(shí)際上,通過去耦電容一樣會(huì)有噪聲,后面會(huì)講到)。

電容去耦原理

實(shí)際電路中,我們會(huì)看到芯片周圍布滿了電容,這些電容稱為去耦電容,為當(dāng)前硬件設(shè)計(jì)中解決噪聲問題的主要方式。我們可以通過下面兩種方式來對(duì)電容去耦有個(gè)初步的理解。

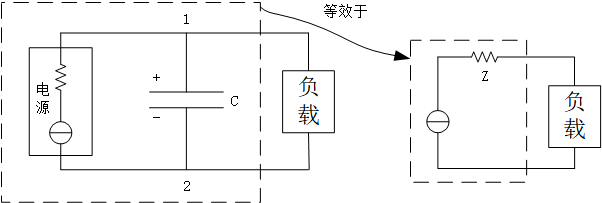

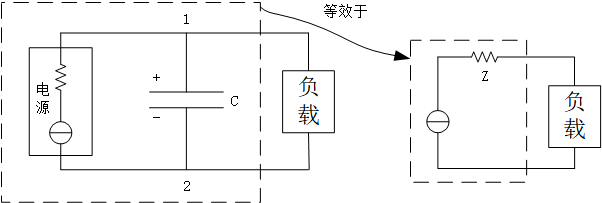

1、阻抗角度

可以通過一張圖來理解:

首先,我們對(duì)PDN的要求就是不論負(fù)載端瞬態(tài)電流如何變化,都得保證負(fù)載兩端電壓的穩(wěn)定,負(fù)載端電壓的變化要盡可能的小。依據(jù)等效電路,可以得到△U=Z*△I(此時(shí)電源為理想電源,阻抗都由Z來等效了,理想電源輸出的電壓是恒定的,那么z與負(fù)載就會(huì)形成一個(gè)分壓效果,進(jìn)而影響負(fù)載兩端電壓的穩(wěn)定)。由于瞬態(tài)電流是動(dòng)態(tài)的,有交流特性,而去耦電容剛好在交流條件下表現(xiàn)為低阻抗(再極端點(diǎn),因?yàn)殡娮璨⒙?lián)阻抗會(huì)減小,也就是電容并的越多,等效阻抗就越小),即去耦電容能夠減小Z,進(jìn)而減小電源噪聲。

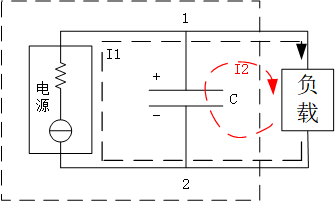

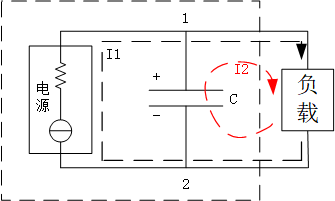

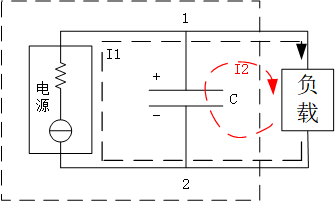

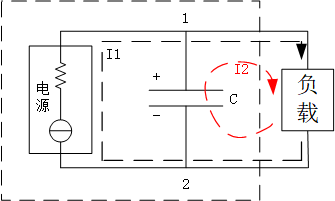

2、儲(chǔ)能角度

同樣可以通過一張圖來理解:

上圖可以看到,負(fù)載相當(dāng)于同時(shí)由電源和電容進(jìn)行供電,當(dāng)負(fù)載電流穩(wěn)定的時(shí)候,I2為0,負(fù)載由電源進(jìn)行供電,并且電容電壓等于電源供電電壓,此時(shí)電容是存儲(chǔ)滿了電量的,當(dāng)負(fù)載電流變化的時(shí)候,由于電源存在響應(yīng)時(shí)間,無法立即響應(yīng)負(fù)載電流的變化,因此負(fù)載端電壓會(huì)下降,此時(shí)電容感受到負(fù)載端電壓的變化,此時(shí)電容開始放電,I2不再為0,開始為負(fù)載供電,而I=C*dV/dt,當(dāng)電容的C足夠大的時(shí)候,只需要很小的dV就能夠提供很大的電流,用以滿足負(fù)載變化的需求,進(jìn)而控制負(fù)載端電壓變化不至于過大。

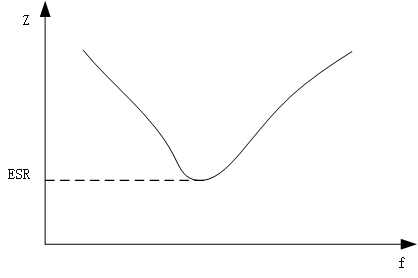

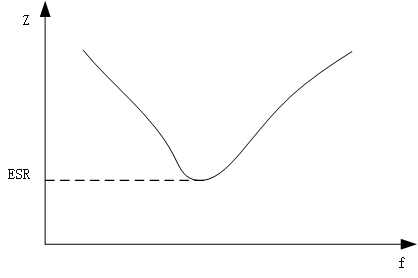

電容阻抗特性

電容簡化模型如下:

ESR一般為電極,電解質(zhì)的等效電阻,C為電容的容值,ESL為電極和端子的等效電感。

因此一個(gè)電容的特性阻抗Z可以表示為:

Z=ESR+j2πfESL+1/j2πfC=ESR+j(2πfESL- 1/2πfC)

當(dāng)頻率很低的時(shí)候,2πfESL遠(yuǎn)小于1/2πfC,電流超前于電壓,電容的阻抗隨頻率增加而減小,電容呈現(xiàn)容性;當(dāng)頻率很高的時(shí)候,2πfESL大于1/2πfC,電流滯后于電壓,電容的阻抗隨頻率增加而增大,電容呈現(xiàn)感性;2πfESL=1/2πfC,f= 1/(2π√(ESLC)),電容呈現(xiàn)純電阻特性,此時(shí)電容阻抗最小,該頻率點(diǎn)也稱為電容的自諧振頻率。因此,去耦電容實(shí)際上都有一定的工作頻率范圍,只有在這個(gè)范圍內(nèi),去耦電容的去耦效果才比較好。

復(fù)阻抗概念

Z=R+jX=R+j(XL-XC)

當(dāng)X>0時(shí),XL>XC,電壓超前于電流,電路呈感性;

當(dāng)X<0時(shí),XL<XC,電壓滯后于電流,電路呈容性;

當(dāng)X=0時(shí),XL=XC,電壓與電流同相,電路呈純阻性。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

相關(guān)閱讀