了解基于電源抑制參數(shù)的去耦需求解析

本文將討論如何通過(guò)電源去耦來(lái)保持電源進(jìn)入集成電路(IC)的各點(diǎn)的低阻抗。

諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個(gè)或兩個(gè)以上電源引腳。對(duì)于單電源器件,其中一個(gè)引腳通常連接到地。諸如ADC和DAC等混合信號(hào)器件可以具有模擬和數(shù)字電源電壓以及 I/O電壓。像FPGA這樣的數(shù)字IC還可以具有多個(gè)電源電壓,例如內(nèi)核電壓、存儲(chǔ)器電壓和I/O電壓。

不管電源引腳的數(shù)量如何,IC數(shù)據(jù)手冊(cè)都詳細(xì)說(shuō)明了每路電源的的允許范圍,包括推薦工作范圍和最大絕對(duì)值,而且為了保持正常工作和防止損壞,必須遵守這些限制。

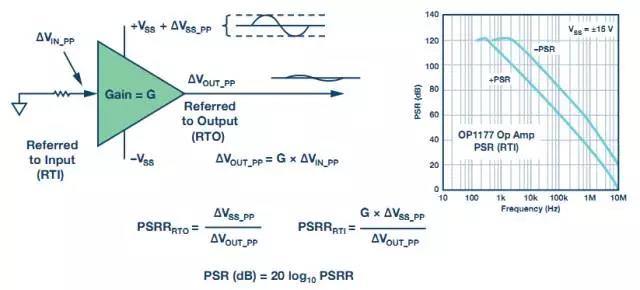

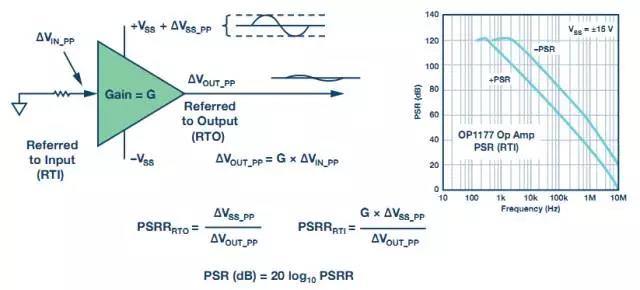

然而,由于噪聲或電源紋波導(dǎo)致的電源電壓的微小變化—即便仍在推薦的工作范圍內(nèi)—也會(huì)導(dǎo)致器件性能下降。例如在放大器中,微小的電源變化會(huì)產(chǎn)生輸入和輸出電壓的微小變化,如圖所示。

放大器的電源抑制顯示輸出電壓對(duì)電源軌變化的靈敏度

如果放大器正在驅(qū)動(dòng)負(fù)載,并且在電源軌上存在無(wú)用阻抗,則負(fù)載電流會(huì)調(diào)制電源軌,從而增加交流信號(hào)中的噪聲和失真。

適當(dāng)?shù)木植咳ヱ钤赑CB上是必不可少的。

典型的4層PCB通常設(shè)計(jì)為接地層、電源層、頂部信號(hào)層和底部信號(hào)層。表面貼裝IC的接地引腳通過(guò)引腳上的過(guò)孔直接連接到接地層,從而最大限度地減少接地連接中的無(wú)用阻抗。

電源軌通常位于電源層,并且路由到IC的各種電源引腳。顯示電源和接地連接的簡(jiǎn)單IC模型如圖2所示。

IC內(nèi)產(chǎn)生的電流流過(guò)走線阻抗Z的電流產(chǎn)生電源電壓VS的變化,這將會(huì)產(chǎn)生各種類型的性能降低。

通過(guò)使用盡可能短的連接,將適當(dāng)類型的局部去耦電容直接連接到電源引腳和接地層之間,可以最大限度地降低對(duì)功率噪聲和紋波的靈敏度。去耦電容用作瞬態(tài)電流的電荷庫(kù),并將其直接分流到地,從而在IC上保持恒定的電源電壓。雖然回路電流路徑通過(guò)接地層,但由于接地層阻抗較低,回路電流一般不會(huì)產(chǎn)生明顯的誤差電壓。

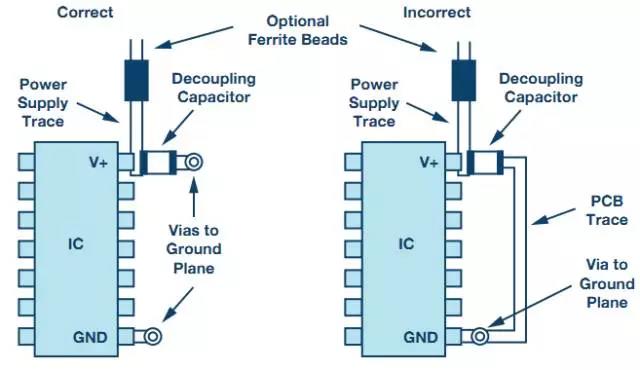

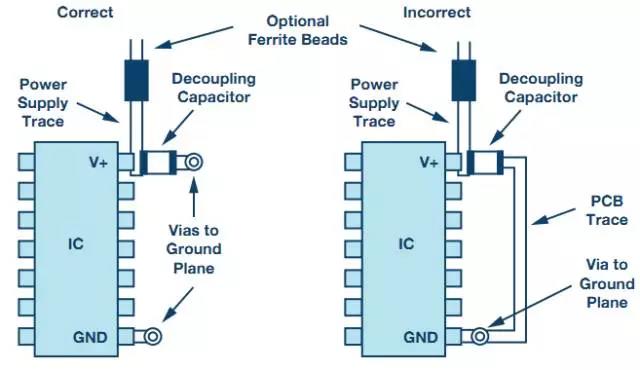

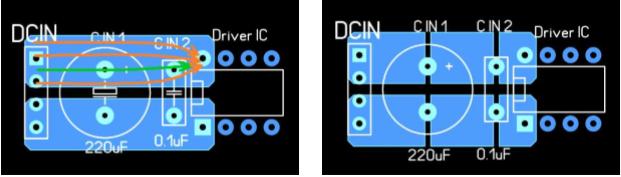

下圖顯示了高頻去耦電容必須盡可能靠近芯片的情況。否則,連接走線的電感將對(duì)去耦的有效性產(chǎn)生不利影響。

高頻去耦電容的正確和錯(cuò)誤放置

圖左側(cè),電源引腳和接地連接都可能短,所以是最有效的配置。然而在圖右側(cè)中,PCB走線內(nèi)的額外電感和電阻將造成去耦方案的有效性降低,且增加封閉環(huán)路可能造成干擾問(wèn)題。

電源去耦路徑

去耦電容擺放的位置及PCB走線是相當(dāng)重要的,不合理的走線可能會(huì)使去耦電容幾乎沒(méi)有起到作用

在計(jì)算并聯(lián)有電容的負(fù)載發(fā)生階躍,負(fù)載兩端的電壓變化情況時(shí),有公式 ΔU=IR

其中

I 為負(fù)載電流,R為電容的等效串聯(lián)電阻??梢姡ヱ铍娙莸牡刃Т?lián)電阻越小,負(fù)載階躍時(shí)電壓的變化量越小。平時(shí)使用的電解電容具有一定的R,這是不可避免的,只能通過(guò)優(yōu)化布線來(lái)減少PCB走線對(duì)R的影響。

在 PCB 布局時(shí),應(yīng)檢查去耦電容的放置是否符合以下原則:

(1)將電解電容放置在電源芯片或大電流負(fù)載的附近;

(2)0.1uF 瓷片電容最靠近芯片引腳放置;

(3)電源走線經(jīng)過(guò)電容引腳之后再到達(dá)芯片供電引腳。

在設(shè)計(jì)大電流PCB時(shí),經(jīng)常需要使用多邊形鋪銅工具來(lái)布線,這可以增大走線所承受的電流,但有一些需要注意的地方。

走線加寬后,電流路徑的寬度增加,于是,在左圖中,大部分的電流沿著橙色箭頭的方向流入芯片,僅有小部分電流由綠色箭頭,流經(jīng)去耦電容,再流入芯片,這回降低電容的去耦作用。因此,如右圖所示,在電容的引腳處劃開,可以使電流先流經(jīng)去耦電容,在流入芯片。

在實(shí)際電路板的布線中,最好是沿著電路的電流流動(dòng)方向來(lái)進(jìn)行電路的設(shè)計(jì)。

選擇正確類型的去耦電容

低頻噪聲去耦通常需要用電解電容(典型值為1µF至100µF),以此作為低頻瞬態(tài)電流的電荷庫(kù)。將低電感表面貼裝陶瓷電容(典型值為0.01µF至0.1µF)直接連接到IC電源引腳,可最大程度地抑制高頻電源噪聲。所有去耦電容必須直接連接到低電感接地層才有效。此連接需要短走線或過(guò)孔,以便將額外串聯(lián)電感降至最低。

大多數(shù)IC數(shù)據(jù)手冊(cè)在應(yīng)用部分說(shuō)明了推薦的電源去耦電路,用戶應(yīng)始終遵循這些建議,以確保器件正常工作。

鐵氧體磁珠并非始終必要,但可以增強(qiáng)高頻噪聲隔離和去耦,通常較為有利。這里可能需要驗(yàn)證磁珠永遠(yuǎn)不會(huì)飽和,特別是在運(yùn)算放大器驅(qū)動(dòng)高輸出電流時(shí)。當(dāng)鐵氧體飽和時(shí),它就會(huì)變?yōu)榉蔷€性,失去濾波特性。

在為去耦應(yīng)用選擇合適的類型時(shí),需要仔細(xì)考慮由于寄生電阻和電感產(chǎn)生的非理想電容性能。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹