硅柵MOS結(jié)構(gòu)詳細(xì)解析

硅柵MOS結(jié)構(gòu):在MOS-IC的早期產(chǎn)品中,廣泛使用金屬AI作為柵極。例如上世紀(jì)60年代中期第一只MOS-IC即為p溝增強(qiáng)型A1柵器件。但隨著MOS-IC規(guī)模的增大、線條的變細(xì)性能要求的提高,Al柵MOS技術(shù)逐漸被硅柵MOS所代替。

硅柵MOS結(jié)構(gòu):工藝的特點(diǎn)

硅柵工藝的發(fā)展和應(yīng)用,同以下幾個(gè)方面的原因緊密相連:

(1)我們知道Al柵的淀積必須在完成了硅器件所有的高溫過(guò)程以后進(jìn)行。因此它務(wù)必要同IC中器件的源、漏區(qū)對(duì)準(zhǔn)。在套準(zhǔn)精度的限制之下,棚區(qū)的尺寸必須比預(yù)定的溝道長(zhǎng)度更長(zhǎng),以便覆蓋住源、漏區(qū)。

這導(dǎo)致了集成密度的下降和寄生效應(yīng)的增加。由于多晶硅與硅襯底是同一種材料,具有相同的熔點(diǎn),它可以在形成漏、源區(qū)之前淀積上去。同時(shí)硅柵本身又可作為離子注入的掩膜,幾乎可完美地形成所需的器件溝道區(qū)。

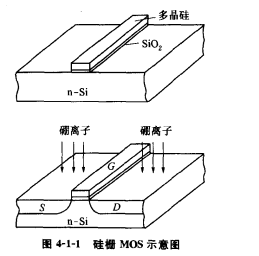

這種“自對(duì)準(zhǔn)”的特點(diǎn)不僅簡(jiǎn)化了制備工藝,而且增加了器件密度,減少了柵-源間和柵-漏間的寄生電容。這一特點(diǎn)的示意圖如圖4-1-1所示。在硅襯底上先要形成薄的柵氧化區(qū),隨后淀積多晶硅并圖形化,隨后經(jīng)由離子注入形成漏、源區(qū)。在硅柵之下沒(méi)有注入離子,形成所需的溝道。

(2)由于硅柵與硅襯底之間的接觸功函數(shù)的差別為零,從而使閾值電壓負(fù)得更少一點(diǎn),減少了p溝MOS的閾值電壓絕對(duì)值。如可從-4V下降為-2V。這樣使硅柵MOSIC可以同其他數(shù)字電路相兼容,如TTL電路等。

(3)由于多晶硅能忍受高溫,它可以完全地被SiO2層封包起來(lái),使多晶硅不僅能作為柵電極用,而且可以作為互連線用。在多層布線技術(shù)中,它可以被另外的金屬層或多晶硅層所穿過(guò)。

使IC設(shè)計(jì)中的布線更為方便和緊湊。因多晶硅能忍受高溫.它又可允許被覆蓋摻磷SiO2等介質(zhì)膜,以完成金屬化之前所必須的表面平坦化過(guò)程。

硅柵MOS結(jié)構(gòu):硅柵MOS技術(shù)中最大的不利因素是它比Al柵材料有高得多的電阻率。即使在高摻雜的情況下,0.5μm厚的多晶硅電阻率約為20Ω/sq。這同相應(yīng)厚度的Al材料相比要大約400倍。高的電阻率勢(shì)必造成更長(zhǎng)的RC時(shí)間常數(shù)以及芯片中較嚴(yán)重的直流電壓的變化。

為克服這一缺點(diǎn),常在多晶硅上淀積耐熔金屬或硅化物薄膜。這類薄膜的薄層電阻率為1Ω/sq,可以明顯地減少多晶硅的高阻帶來(lái)的負(fù)面影響。但是,盡管存在上述的限制,硅柵MOS技術(shù)已經(jīng)成為當(dāng)今MOS-IC技術(shù)中的主流技術(shù)。

場(chǎng)區(qū)、有源區(qū)和等平面工藝

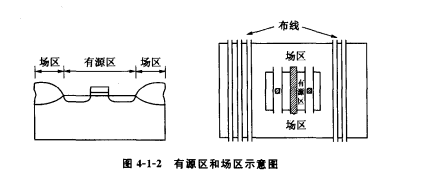

在MOS-IC的芯片內(nèi),從工藝結(jié)構(gòu)來(lái)看,可以分為兩個(gè)區(qū)域:場(chǎng)區(qū)和有源區(qū)。有源區(qū)是用以制作MOS晶體管、電阻或電容的區(qū)域。在此區(qū)域內(nèi)不存在很厚的熱生長(zhǎng)SiO2 層,只存在制作器件必須的薄氧化層和當(dāng)隔離介質(zhì)中的CVD淀積的SiO2層。

在此區(qū)域內(nèi),除器件所必須的引出線外,一般不能通過(guò)其他導(dǎo)電層。在有源區(qū)之外的就是場(chǎng)區(qū),這一區(qū)域由很厚的熱生長(zhǎng)SiO2層組成,大量的金屬布線穿越其間,芯片的眾多金屬引線腳也布置在它上面。圖4-1-2是有源區(qū)和場(chǎng)區(qū)的示意圖。

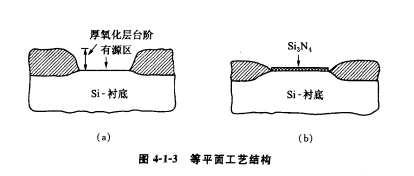

在普通的集成電路平面工藝中,SiO2層作為絕緣介質(zhì)和摻雜時(shí)的掩蔽材料,發(fā)揮了關(guān)鍵的作用。MOS-IC的場(chǎng)區(qū)由熱生長(zhǎng)SiO2層組成,而有源區(qū)則無(wú)這樣的厚氧化層。熱生長(zhǎng)SiO2層的過(guò)程,要消耗硅襯底材料。

在形成有源區(qū)時(shí),必須將有源區(qū)上的厚SiO2層除去。這樣,在有源區(qū)和場(chǎng)區(qū)之間形成一個(gè)明顯的臺(tái)階, 如圖4-1-3所示。這樣的高臺(tái)階對(duì)從有源區(qū)引出的布線是不利的,金屬布線在臺(tái)階處容易斷裂,造成器件的失效。

用“等平面工藝”很容易解決這一問(wèn)題。只要在有源區(qū)的區(qū)域上淀積一層Si3N4以保護(hù)這一區(qū)不被熱氧化,從而使這一區(qū)域的硅平面和四周的厚氧化層平面維持在較接近的水平,大大減少了布線跨越的臺(tái)階。一種叫全凹陷氧化工藝(FUROX)提供了較完美的等平面氧化技術(shù)。

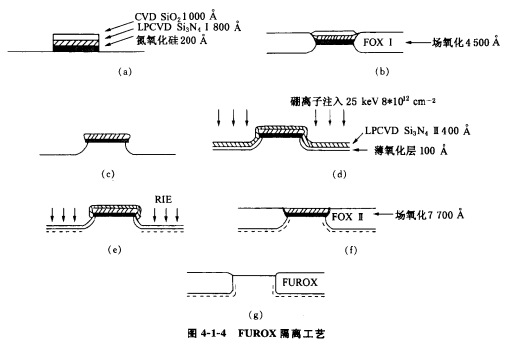

圖4-1-4示出了這一工藝的主要步驟。在有源區(qū)部分依次熱生長(zhǎng)氮氧化硅層200A,LPCVD生長(zhǎng)Si3N4 800A,CVD淀積SiO2 1000A。隨后在場(chǎng)區(qū)熱生長(zhǎng)siO2 4500A。然后用化學(xué)腐蝕方法除去以形成一個(gè)槽。

生長(zhǎng)第二層100A厚的氧化硅層并用CVD方法淀積400A厚的氮化硅層。進(jìn)行自對(duì)準(zhǔn)場(chǎng)區(qū)的“溝道阻止”硼注入。用離子反應(yīng)刻蝕方法各向異性地腐蝕掉第二層氮化硅層,但仍保留側(cè)墻處的Si3N4層以作為掩蔽氧化用。接著進(jìn)行第二次場(chǎng)氧化,形成一個(gè)無(wú)缺陷,接近“零鳥嘴”,全凹陷的非常平坦的氧化區(qū)。