CMOS介紹

CMOS是Complementary Metal Oxide Semiconductor(互補金屬氧化物半導體)的縮寫。它是指制造大規(guī)模集成電路芯片用的一種技術或用這種技術制造出來的芯片,是電腦主板上的一塊可讀寫的RAM芯片。

因為可讀寫的特性,所以在電腦主板上用來保存BIOS設置完電腦硬件參數(shù)后的數(shù)據,這個芯片僅僅是用來存放數(shù)據的。而對BIOS中各項參數(shù)的設定要通過專門的程序。

BIOS設置程序一般都被廠商整合在芯片中,在開機時通過特定的按鍵就可進入BIOS設置程序,方便地對系統(tǒng)進行設置。因此BIOS設置有時也被叫做CMOS設置。

CMOS集成電路

CMOS集成電路特性

(1)功耗低

CMOS集成電路采用場效應管,且都是互補結構,工作時兩個串聯(lián)的場效應管總是處于一個管導通,另一個管截止的狀態(tài),電路靜態(tài)功耗理論上為零。

實際上,由于存在漏電流,CMOS電路尚有微量靜態(tài)功耗。單個門電路的功耗典型值僅為20mW,動態(tài)功耗(在1MHz工作頻率時)也僅為幾mW。

(2)工作電壓范圍寬

CMOS集成電路供電簡單,供電電源體積小,基本上不需穩(wěn)壓。國產CC4000系列的集成電路,可在3~18V電壓下正常工作。

(3)邏輯擺幅大CMOS集成電路的邏輯高電平“1”、邏輯低電平“0”分別接近于電源高電位VDD及電影低電位VSS。當VDD=15V,VSS=0V時,輸出邏輯擺幅近似15V。因此,CMOS集成電路的電壓利用系數(shù)在各類集成電路中指標是較高的。

(4)抗干擾能力強

CMOS集成電路的電壓噪聲容限的典型值為電源電壓的45%,保證值為電源電壓的30%。隨著電源電壓的增加,噪聲容限電壓的絕對值將成比例增加。對于VDD=15V的供電電壓(當VSS=0V時),電路將有7V左右的噪聲容限。

(5)輸入阻抗高

CMOS集成電路的輸入端一般都是由保護二極管和串聯(lián)電阻構成的保護網絡,故比一般場效應管的輸入電阻稍小,

但在正常工作電壓范圍內,這些保護二極管均處于反向偏置狀態(tài),直流輸入阻抗取決于這些二極管的泄露電流,通常情況下,等效輸入阻抗高達103~1011Ω,因此CMOS集成電路幾乎不消耗驅動電路的功率。

(6)溫度穩(wěn)定性能好

由于CMOS集成電路的功耗很低,內部發(fā)熱量少,而且,CMOS電路線路結構和電氣參數(shù)都具有對稱性,在溫度環(huán)境發(fā)生變化時,某些參數(shù)能起到自動補償作用,因而CMOS集成電路的溫度特性非常好。

一般陶瓷金屬封裝的電路,工作溫度為-55 ~ +125℃;塑料封裝的電路工作溫度范圍為-45 ~ +85℃。

(7)扇出能力強

扇出能力是用電路輸出端所能帶動的輸入端數(shù)來表示的。由于CMOS集成電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS集成電路用來驅動同類型,如不考慮速度,一般可以驅動50個以上的輸入端。

(8)抗輻射能力強

CMOS集成電路中的基本器件是MOS晶體管,屬于多數(shù)載流子導電器件。各種射線、輻射對其導電性能的影響都有限,因而特別適用于制作航天及核實驗設備。

(9)可控性好

CMOS集成電路輸出波形的上升和下降時間可以控制,其輸出的上升和下降時間的典型值為電路傳輸延遲時間的125%~140%。

(10)接口方便

因為CMOS集成電路的輸入阻抗高和輸出擺幅大,所以易于被其他電路所驅動,也容易驅動其他類型的電路或器件。

CMOS集成電路的工作原理

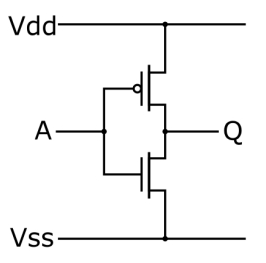

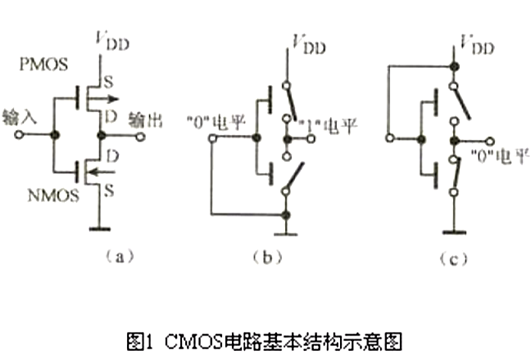

以CMOS集成電路中的一個最基本電路——反相器(其他復雜的CMOS集成電路大多是由反相器單元組合而成)為例,分析CMOS集成電路的工作過程。

利用一個P溝道MOS管和一個N溝道MOS管互補連接就構成了一個最基本的反相器單元電路如附圖所示。圖2中VDD為正電源端,VSS為負電源端。電路設計采用正邏輯方法,即邏輯“1”為高電平,邏輯“0”為低電平。

圖2中,當輸入電壓VI為低電平“0”(VSS)時,N溝道MOS管的柵-源電壓VGSN=0V(源極和襯底一起接VSS),由于是增強型管,所以管子截止,而P溝道MOS管的柵-源電壓VGSN=VSS—VDD。若|VSS—VDD|>|VTP|(MOS管開啟電壓),則P溝道MOS管導通,所以輸出電壓V0為高電平“1”(VDD),實現(xiàn)了輸入和輸出的反相功能。

當輸入電壓VI為底電平“1”(VDD)時,VGSN=(VDD—VSS)。若(VDD—VSS)>VGSN,則N溝道MOS管導通,此時VGSN=0V,P溝道MOS管截止,所以輸出電壓V0為低電平“0”(VSS),與VI互為反相關系。

由上述分析可知,當輸入信號為“0”或“1”的穩(wěn)定狀態(tài)時,電路中的兩個MOS管總有一個處于截止狀態(tài),使得VDD和VSS之間無低阻抗直流通路,因此靜態(tài)功耗極小。這便是CMOS集成電路最主要的特點。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280